- 您现在的位置:买卖IC网 > Sheet目录3753 > ATMEGA169P-16MCHR (Atmel)MCU AVR 16KB FLASH 16MHZ 64-VQFN

88

8018P–AVR–08/10

ATmega169P

13.4

Register Description for I/O-Ports

13.4.1

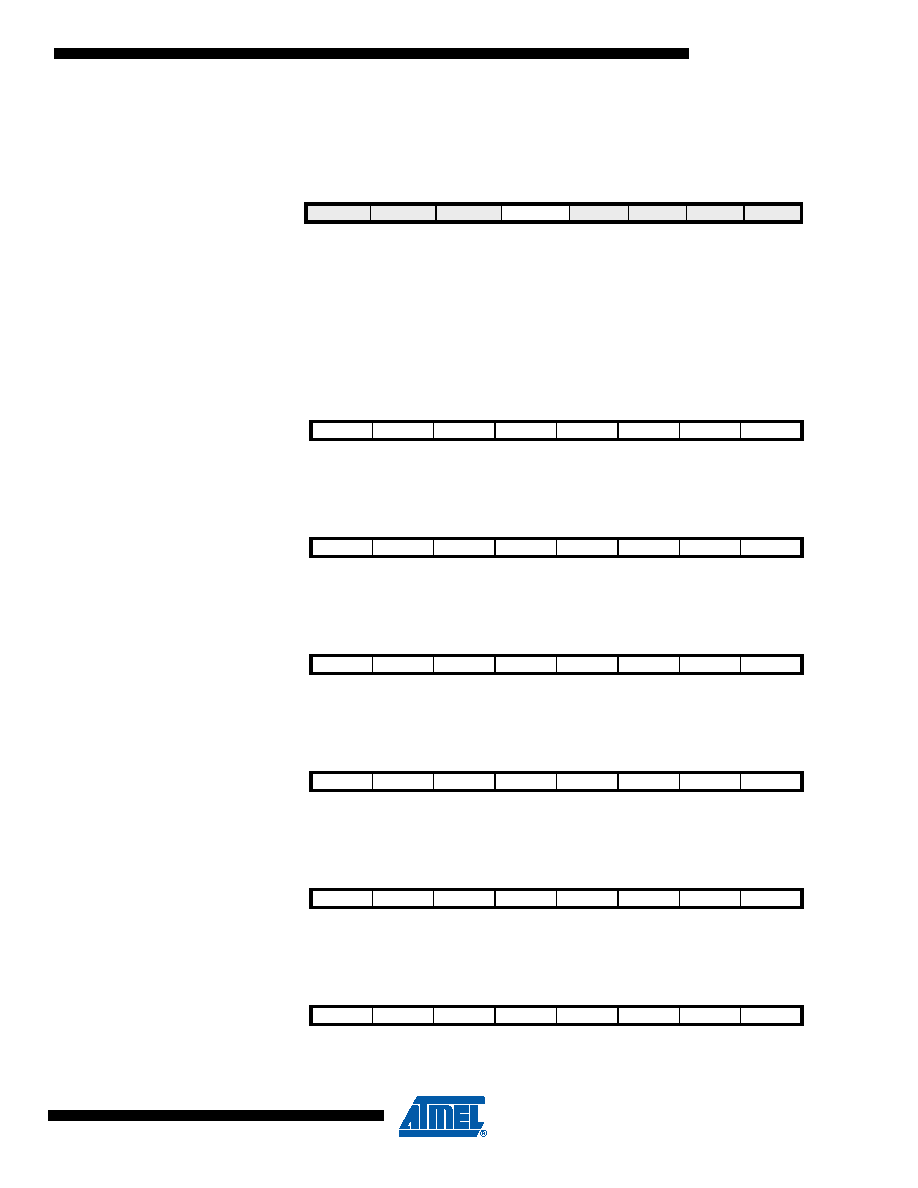

MCUCR – MCU Control Register

Bit 4 – PUD: Pull-up Disable

When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and

PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01). See ”Con-

figuring the Pin” on page 66 for more details about this feature.

13.4.2

PORTA – Port A Data Register

13.4.3

DDRA – Port A Data Direction Register

13.4.4

PINA – Port A Input Pins Address

13.4.5

PORTB – Port B Data Register

13.4.6

DDRB – Port B Data Direction Register

13.4.7

PINB – Port B Input Pins Address

Bit

7

6

5

4

3

2

1

0

0x35 (0x55)

JTD

-

-PUD

–

IVSEL

IVCE

MCUCR

Read/Write

R/W

R

R/W

R

R/W

Initial Value

0

Bit

765

43

210

0x02 (0x22)

PORTA7

PORTA6

PORTA5

PORTA4

PORTA3

PORTA2

PORTA1

PORTA0

PORTA

Read/Write

R/W

Initial Value

0

Bit

765

43

210

0x01 (0x21)

DDA7

DDA6

DDA5

DDA4

DDA3

DDA2

DDA1

DDA0

DDRA

Read/Write

R/W

Initial Value

0

Bit

765

43

210

0x00 (0x20)

PINA7

PINA6

PINA5

PINA4

PINA3

PINA2

PINA1

PINA0

PINA

Read/Write

R/W

Initial Value

N/A

Bit

765

43

210

0x05 (0x25)

PORTB7

PORTB6

PORTB5

PORTB4

PORTB3

PORTB2

PORTB1

PORTB0

PORTB

Read/Write

R/W

Initial Value

0

Bit

765

43

210

0x04 (0x24)

DDB7

DDB6

DDB5

DDB4

DDB3

DDB2

DDB1

DDB0

DDRB

Read/Write

R/W

Initial Value

0

Bit

765

43

210

0x03 (0x23)

PINB7

PINB6

PINB5

PINB4

PINB3

PINB2

PINB1

PINB0

PINB

Read/Write

R/W

Initial Value

N/A

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

2-1546217-0

TERM BLK RCPT 20POS SIDE 5.08MM

1-1546217-9

TERM BLK RCPT 19POS SIDE 5.08MM

1-1546217-8

TERM BLK RCPT 18POS SIDE 5.08MM

1-1546217-7

TERM BLK RCPT 17POS SIDE 5.08MM

1-1546217-6

TERM BLK RCPT 16POS SIDE 5.08MM

1-1546217-5

TERM BLK RCPT 15POS SIDE 5.08MM

1-1546217-4

TERM BLK RCPT 14POS SIDE 5.08MM

1-1546217-3

TERM BLK RCPT 13POS SIDE 5.08MM

相关代理商/技术参数

ATMEGA169P-16MCU

功能描述:8位微控制器 -MCU AVR 16KB, 512B EE 16MHz 1KB SRAM, 5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU

功能描述:8位微控制器 -MCU AVR 16K FLASH 512B EE 1K SRAM LCD ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU SL383

制造商:Atmel Corporation 功能描述:MCU 8BIT ATMEGA RISC 16KB FLASH 3.3V/5V 64PIN MLF - Tape and Reel

ATMEGA169P-16MUR

功能描述:8位微控制器 -MCU AVR LCD 16KB FLSH EE 512B 1KB SRAM-16MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-8AU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169P-8MU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA_1

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:High Endurance Non-volatile Memory segments